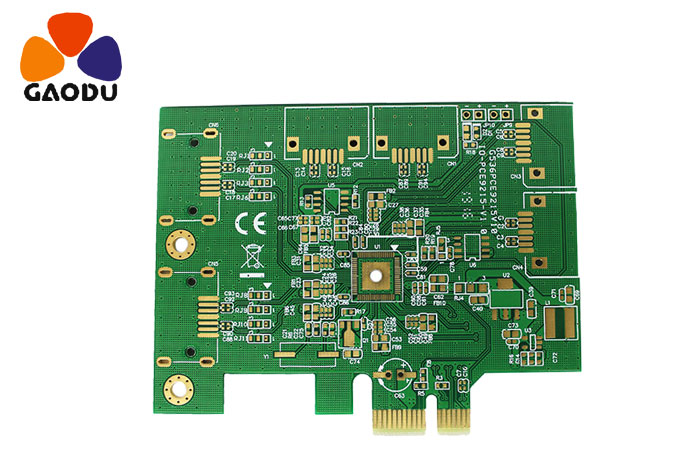

为客户提供最专业的PCB行业服务

- 服务热线:13824363925

行业资讯

行业资讯

0

2020-09-26 11:46:41

2020-09-26 11:46:41

1.降低核心电压也会降低噪声容限;

2.串扰是电磁场耦合造成的;

3.串扰会随距离的平方迅速减小,其影响程度与噪声源的信号电压及其邻近度有关。

4.同步总线具有很强的抗串扰能力,它只会在时钟开启的瞬间影响很短的窗口范围;

5.如果电源电压从3.3V降到1.5V,允许的噪声容限会降低一半以上;

6.差分技术不存在单端技术的噪声容限问题,因为共模抑制;

7.受影响线路上的总串扰是附近多个串扰源的总和;

8.带状线结构中没有正向串扰,串扰的幅度会显著降低;

9.模拟应该将所有信号的最大串扰设置为150mV;除非频率很高,否则同步总线同组信号的串扰可以忽略不计;

10.正向和反向串扰可以通过将干扰源与受影响的布线分开或者通过减小平面上方/下方的电介质厚度来减小。

双面板免费加费,四层板加急打样,厚铜电路板打样