- 服务热线:13824363925

行业资讯

行业资讯

0

2020-09-12 18:22:01

2020-09-12 18:22:01

背景技术:

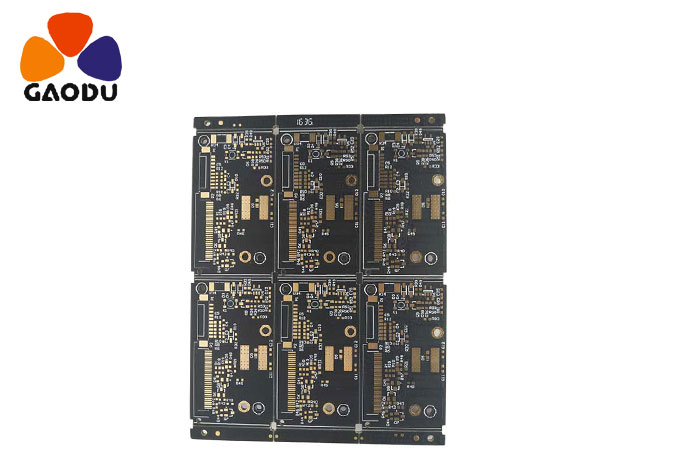

随着高速、高频信号传输的发展,信号的上升时间越来越短,信号在PCB中的传输频率和传输速率也越来越高。同时,信号传输的高速化和高频化发展使得传输线效应越来越严重,在传输过程中更容易出现串扰、反射等问题。为了保持信号传输的完整性,要求PCB在设计和制造过程中保证阻抗匹配。因此,阻抗是高速PCB设计制造中需要严格控制的重要指标之一。

对于PCB阻抗控制,一般需要控制PCB上信号线的阻抗和不同层通过过孔电连接时过孔的阻抗。传统上,阻抗测试条设计在电路板的生产拼版板边缘,通过测试阻抗测试条的阻抗可以判断产品的线路阻抗是否合格。当需要控制过孔阻抗时,不仅要测试线棒的线路阻抗,还要在PCB版图的图形中找到有孔的阻抗线来测试过孔阻抗,进而判断线路阻抗和过孔阻抗是否满足要求。但是由于PCB布局图形的复杂性和多样性,很难找到符合要求的阻抗线,导致测试工作量大,效率低。

技术实现的要素:

因此,有必要提供一种阻抗测试条和电路板,在阻抗测试时操作简单方便,可以减少测试工作量,提高测量效率。

其技术方案如下:

一种阻抗测试条,包括测试条本体,测试条本体上设有单端电阻抗测试线和/或差分阻抗测试线;

当测试条本体设有单端电阻抗测试线时,单端电阻抗测试线包括设置在测试条本体不同层上的第一通孔、第一单端阻抗线和第二单端阻抗线,第一单端阻抗线的第一端和第二单端阻抗线的第一端通过第一通孔转移, 测试条本体位于第一单端阻抗线和/或第二单端阻抗线;的第二端。第二端设有第一测试孔

当差分阻抗测试线设置在测试条本体上时,差分阻抗测试线包括设置在测试条本体不同层上的第二过孔和第一差分阻抗线和第二差分阻抗线,第一差分阻抗线的第一端和第二差分阻抗线的第一端通过第二过孔转移,第二测试孔设置在第一差分阻抗线的第二端和/或第二差分阻抗线的第二端的测试条本体上

双面板免费加费,四层板加急打样,厚铜电路板打样